# Characterization of the Outer Barrel modules for the upgrade of the ALICE Inner Tracking System

Benedetto Di Ruzza for the ALICE Collaboration

Department of Physics and Astronomy "Galileo Galilei", University of Padova & INFN

## **Outline**

- ITS Design Objectives

- ITS design elements overview

- Modules test-stand for electrical characterization

- Some prototypes results

# **ITS Upgrade Design Objectives**

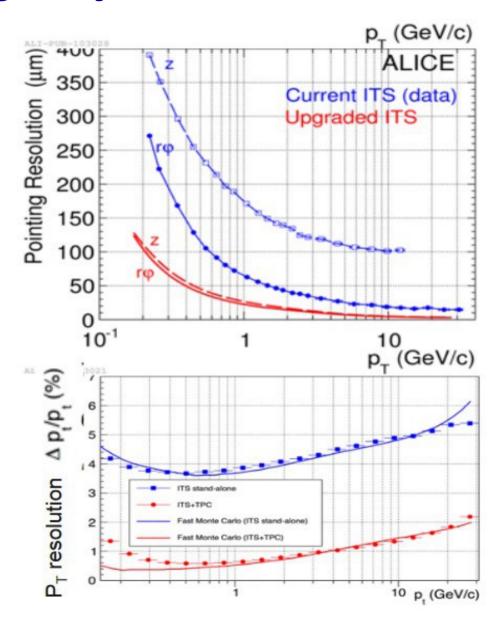

Improve impact parameter resolution by a factor ~3 in r and φ

~5 in z at  $p_T$ =500MeV/c

- get closer to IP: 39mm →22mm (innermost layer)

- reduce material budget: ~1.14% X<sub>0</sub>→

- ~0.3% X<sub>0</sub> (inner layers)

- ~1.0% X<sub>0</sub> (middle and outer layers)

- reduce pixel size:  $50x425\mu m 2 \rightarrow \infty (30x30\mu m^2)$

Improve tracking efficiency and  $p_{\scriptscriptstyle T}$  resolution at low  $p_{\scriptscriptstyle T}$ :

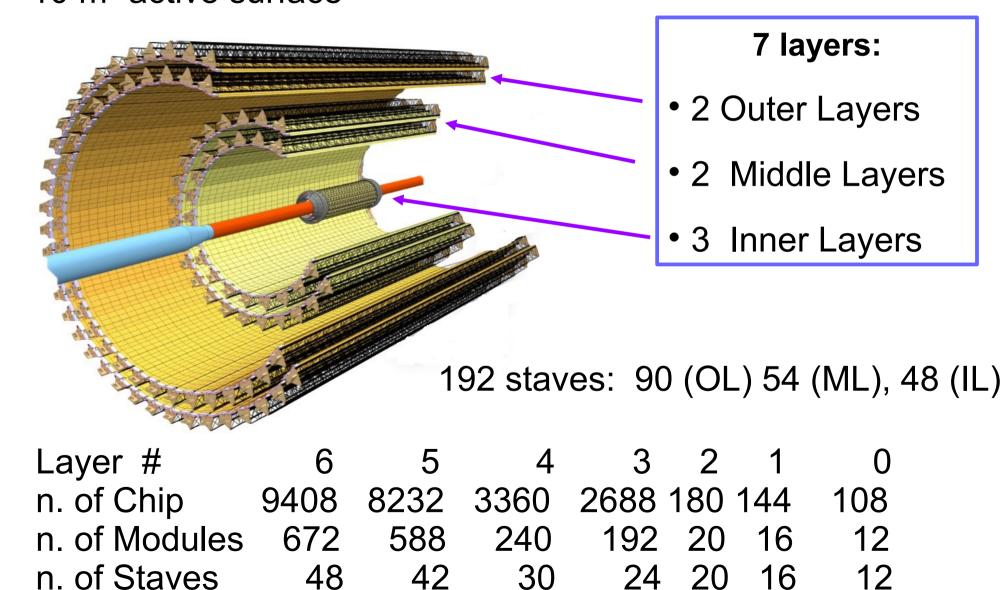

- increase granularity: 6 layers → 7 pixel layers

#### Improve readout rate:

- increase readout rate of Pb-Pb from present 1kHz up to 100 kHz and 400kHz for pp

#### Fast insertion and removal:

possibility to replace non-functioning detector modules during yearly shutdown

# **ITS Upgrade requirements**

#### **Pixel Chip Requirements**

| Parameter                   | Inner Barrel                                               | Outer Barrel                                           | ALPIDE                            |

|-----------------------------|------------------------------------------------------------|--------------------------------------------------------|-----------------------------------|

| Silicon thickness           | 50μm                                                       | 100µm                                                  | ~                                 |

| Spatial resolution          | 5µm                                                        | 10µm                                                   | ~ 5µm                             |

| Chip dimension              | 15mm x 30mm                                                |                                                        | ~                                 |

| Power density               | < 300mW/cm <sup>2</sup>                                    | < 100mW/cm <sup>2</sup>                                | < 40mW/cm <sup>2</sup>            |

| Event-time resolution       | < 30µs                                                     |                                                        | ~ 2µs                             |

| Detection efficiency        | > 99%                                                      |                                                        | ~                                 |

| Fake-hit rate *             | < 10 <sup>-6</sup> /event/pixel                            |                                                        | <<< 10 <sup>-6</sup> /event/pixel |

| NIEL radiation tolerance ** | 1.7x10 <sup>13</sup> 1MeV n <sub>eq</sub> /cm <sup>2</sup> | 10 <sup>12</sup> 1MeV n <sub>eq</sub> /cm <sup>2</sup> | ~                                 |

| TID radiation tolerance **  | 2.7Mrad                                                    | 100krad                                                | tested at 350krad                 |

### **ITS Coverage Requirements**

η coverage:  $|η| \le 1.22$  r coverage: 22 - 400 mm

z coverage: Inner Layers L = 290 mm

Middle Layers L = 900 mm

Outer Layers L = 1500 mm

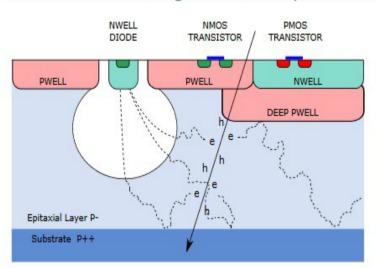

# MAPS Pixel (30x30µm<sup>2</sup>)

## **Building blocks**

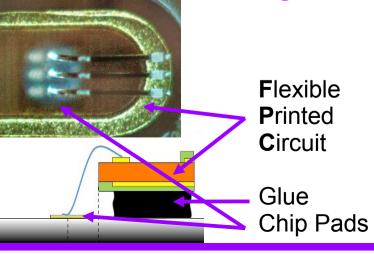

CMOS Pixel Sensor using TowerJazz 0.18µm CMOS Imaging Process

#### Tower Jazz 0.18 μm CMOS

- feature size 180 nm

- metal layers

- → Suited for high-density, low-power

- Gate oxide 3nm

- → Circuit rad-tolerant

ALPIDE Chip: 1024x512 pixels (30x15 mm²)

cross cables (connection to power bus)

single chip

5

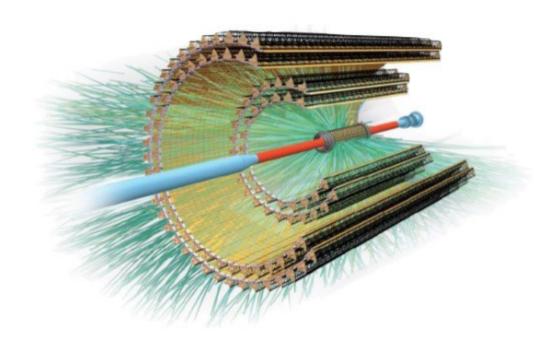

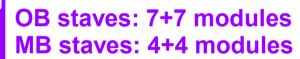

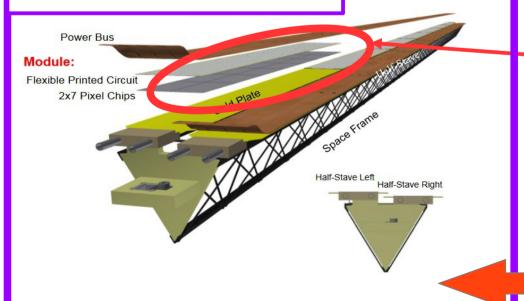

## **ITS Upgrade Overview:**

12.5 Gigapixels ~ 10 m<sup>2</sup> active surface

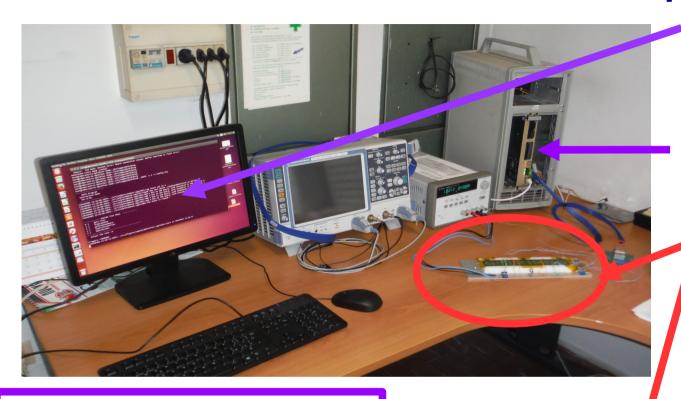

# Module test set-up

Test software (MATE package)

Communication Board (MOSAIC Board)

Module under test (FPC side) Data cables

**Power Cables**

#### **FPC - Chip wire bonding detail**

### **Outer Barrel modules Status**

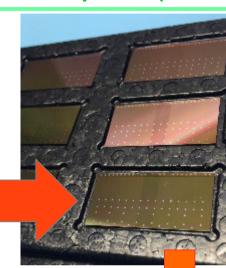

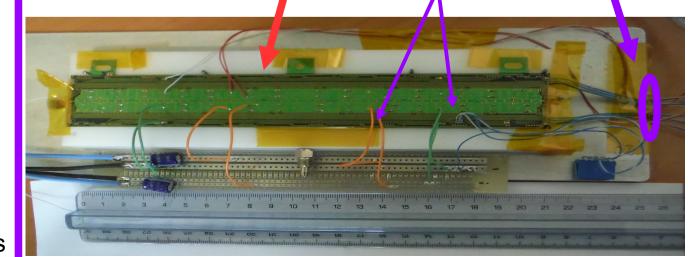

## **OB Modules Prototypes**

So far a series of OB modules prototypes was built using pALPIDE Version 3 chips: 6 modules and 1 OB stave (with 2 modules)

These prototypes were used to define the building modules and stave procedure.

The pALPIDE chip contains a self-injection charge feature that allow to test the read-out chain of every single pixel. This feature, handled by the MATE framework, is used

- to check the inter-modules interconnections (wire bonding integrity)

- to map dead pixels

- to perform the full module readout rates characterization

## Next steps:

Pre-series production is starting (~20 units) with final ALPIDE chips in Oct – Dec 2016

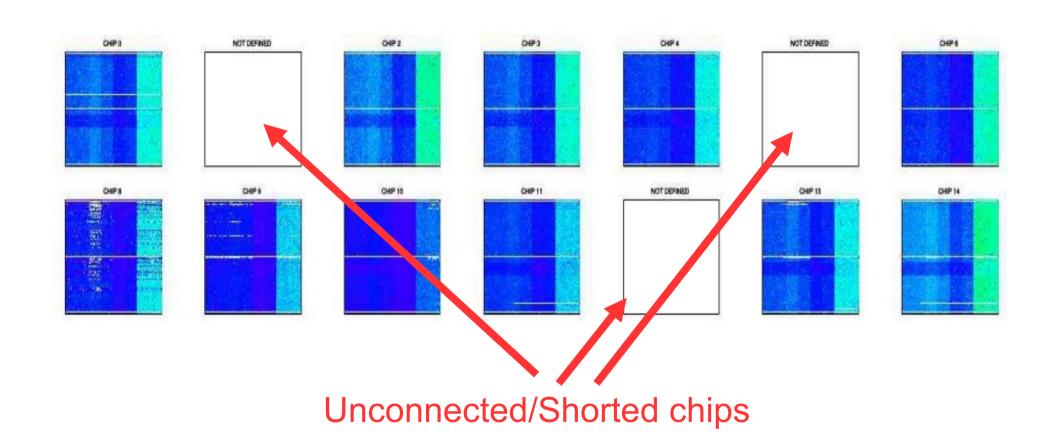

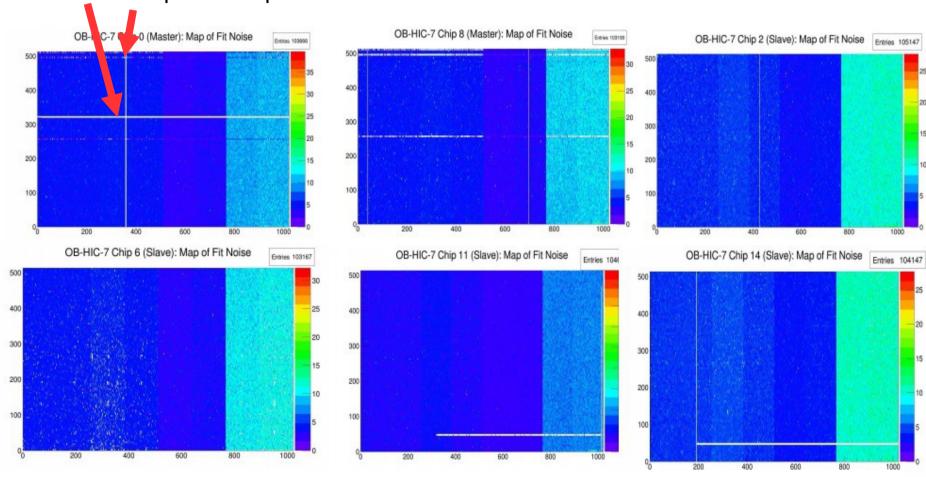

# Some prototype results: global module status

# Some prototype results: single chip details

Broken lines/ bad pixels map

With this setup in ~30 minutes is possible to perform the full module electrical characterization and the full map of bad pixels.

## **Conclusions**

The ALICE ITS upgrade program require the mass production of ~ 1700 Outer Barrel modules.

A procedure was defined in order to perform a fast functional characterization of the produced modules.

This procedure will be implemented in the production of the next final version of the modules.

### References

## ALICE ITS upgrade TDR

https://cds.cern.ch/record/1625842?ln=en

## The upgrade of the ALICE ITS

by Stefania Beole, VERTEX 2016 Conference https://indico.cern.ch/event/452781/contributions/ 2297487/attachments/1343570/2024447/VERTEX2016\_beole.pdf

## **MOSAIC** Board description

by Giuseppe De Robertis, MPGD 2015 Conferece, Trieste 12-15 October 2015 https://agenda.infn.it/contributionDisplay.py?contribId=86&sessionId=8&confId=8839